Difference between r1.7 and the current

@@ -1,11 +1,8 @@

= Nand2Tetris =

* 스터디 소개 :

* 컴퓨터의 최하위 레벨 계층인 논리회로(하드웨어)단부터 OS와 high level language까지 두루두루 섭렵하고 실습하여 최종에는 테트리스를 만드는것이 목표인 스터디입니다.

* 스터디에 사용하는 사이트 -> http://www.nand2tetris.org/

@@ -35,12 +32,13 @@

* Chapter1

* 기본적인 논리 게이트를 공부함.

* Nand gate를 primitive gate로 놓고, 나머지 논리 게이트 Not, And, Or, Xor, Mux, Demux 등을 Nand만으로 구현.

* Mux나 Demux같은 경우, 입력이나 출력이 너무 많을 경우, 작은 규모의 Mux를 여러 개 이용해서 큰 규모의 Mux를 구현해도 된다. 예를 들면, 4way Mux는 2Way Mux 3개를 이용해서 구현할 수 있다.

* HDL Code

* Not Gate

{{{CHIP Not2 {

@@ -53,5 +51,489 @@

}

}}}

----

}}}

* And Gate

{{{

CHIP And {

IN a, b;

OUT out;

PARTS:

Nand(a = a, b = b, out = x);

Nand(a = x, b = x, out = out);

}

}}}

* Or Gate

{{{

CHIP Or {

IN a, b;

OUT out;

PARTS:

Nand(a = a, b = a, out = x1);

Nand(a = b, b = b, out = x2);

Nand(a = x1, b = x2, out = out);

}

}}}

* Xor Gate

{{{

CHIP Xor {

IN a, b;

OUT out;

PARTS:

Nand(a = a, b = a, out = nota);

Nand(a = b, b = b, out = notb);

Nand(a = nota, b = b, out = x1);

Nand(a = a, b = notb, out = x2);

Nand(a = x1, b = x2, out = out);

}

}}}

* Mux

{{{

CHIP Mux {

IN a, b, s;

OUT out;

PARTS:

Nand(a = s, b = s, out = nots);

Nand(a = a, b = s, out = x1);

Nand(a = b, b = nots, out = x2);

Nand(a = x1, b = x2, out = out);

}

}}}

* Mux 4way

{{{

CHIP Mux4way {

IN a[4], s[2];

OUT out;

PARTS:

Nand(a = s[0], b = s[0], out = nots0);

Nand(a = s[1], b = s[1], out = nots1);

Nand(a = a[0], b = s[1], out = x0);

Nand(a = a[1], b = nots1, out = x1);

Nand(a = a[2], b = s[1], out = x2);

Nand(a = a[3], b = nots1, out = x3);

Nand(a = x0, b = x1, out = xx0);

Nand(a = x2, b = x3, out = xx1);

Nand(a = xx0, b = s[0], out = xxx0);

Nand(a = xx1, b = nots0, out = xxx1);

Nand(a = xxx0, b = xxx1, out = out);

}

}}}

* Demux

Demux는 다 구현하고서 Mux 4way를 Demux 파일에 써버리는 바람에 날려버림 ㅡㅡ;

=== 다음 시간까지 해야할 일 ===

* Chapter2 읽어오기.

=== 후기 ===

* 쇠뿔도 단김에 빼라는 말이 있듯이, 순식간에 스터디 진행합니다. 학기 끝날 때까지 매주 진행해보려고 하는데, 끝까지 다 할 수 있었으면 좋겠습니다. 뭐 윤환이나 혁준이형 있으니까 잘 진행되겠죠. 이번 시간에 했던 것은 기초 중에 기초인데, 사실 작년 논리회로 시간에 Nand 게이트로 다른 gate 구현하기 따위는 해본적이 없어서 좀 당황도 했습니다. 그리고 그림 그리는 것도 참 간만이고, 다음 시간까지 논리회로 ppt 좀 보고서 와야겠네요. 간단한 4way MUX도 저리 긴데, 사칙연산은 어떻게 해야할지.. 머리가 아픕니다. - [권영기]

* 간만에 논리회로를 다루면서 내가 까먹고 있던 부분이 많다고 느낌니다. 물론 추상화라는 좋은 녀석이 있어서 우리가 모든것을 기억할 필요는 없지만, 그래도 원리를 안다고 해서 안좋을 것 없을듯하네요. nand로 시작해서 nand로 끝나는 시간이었습니다. - [안혁준]

* 지금은 처음부분이라 무난하게 진행했지만... 가면갈수록 어떤식으로 진행될지 난이도에 따라서 왠지 바뀔수도 있으려나...하는 생각이 들었습니다. 그나저나 논리회로 뒷부분은 거의 기억이 없는데... 전공책한번 훝어보고 와야할것같습니다. - [김윤환]

== 10/6(일요일) ==

* 참여자 : [권영기], [김윤환], [안혁준]

=== 공부 내용 ===

* half-adder, full-adder, 16bit-adder, incremental adder, ALU에 대해서 공부하고 구현하였습니다.

* Half-Adder

{{{

CHIP HalfAdder {

IN a, b; // 1-bit inputs

OUT sum, // Right bit of a + b

carry; // Left bit of a + b

PARTS:

And(a = a, b = b, out = carry);

Xor(a = a, b = b, out = sum);

}

}}}

* Full-Adder

{{{

CHIP FullAdder{

IN a, b, c; // 1-bit inputs

OUT sum, // Right bit of a + b + c

carry; // Left bit of a + b + c

PARTS:

// Put you code here:

Xor(a=a, b=b, out=s1);

And(a=a, b=b, out=c1);

Xor(a=s1, b=c, out=sum);

And(a=s1, b=c, out=c2);

Or(a=c1, b=c2, out=carry);

}

}}}

* 16bit Adder

{{{

CHIP Add16 {

IN a[16], b[16];

OUT out[16];

PARTS:

FullAdder(a = a[0], b = b[0], c = false, sum = out[0], carry = c1);

FullAdder(a = a[1], b = b[1], c = c1, sum = out[1], carry = c2);

FullAdder(a = a[2], b = b[2], c = c2, sum = out[2], carry = c3);

FullAdder(a = a[3], b = b[3], c = c3, sum = out[3], carry = c4);

FullAdder(a = a[4], b = b[4], c = c4, sum = out[4], carry = c5);

FullAdder(a = a[5], b = b[5], c = c5, sum = out[5], carry = c6);

FullAdder(a = a[6], b = b[6], c = c6, sum = out[6], carry = c7);

FullAdder(a = a[7], b = b[7], c = c7, sum = out[7], carry = c8);

FullAdder(a = a[8], b = b[8], c = c8, sum = out[8], carry = c9);

FullAdder(a = a[9], b = b[9], c = c9, sum = out[9], carry = c10);

FullAdder(a = a[10], b = b[10], c = c10, sum = out[10], carry = c11);

FullAdder(a = a[11], b = b[11], c = c11, sum = out[11], carry = c12);

FullAdder(a = a[12], b = b[12], c = c12, sum = out[12], carry = c13);

FullAdder(a = a[13], b = b[13], c = c13, sum = out[13], carry = c14);

FullAdder(a = a[14], b = b[14], c = c14, sum = out[14], carry = c15);

FullAdder(a = a[15], b = b[15], c = c15, sum = out[15], carry = c16);

}

}}}

* Incremental

{{{

CHIP Inc16 {

IN a[16];

OUT out[16];

PARTS:

FullAdder(a = a[0], b = false, c = true, sum = out[0], carry = c1);

FullAdder(a = a[1], b = false, c = c1, sum = out[1], carry = c2);

FullAdder(a = a[2], b = false, c = c2, sum = out[2], carry = c3);

FullAdder(a = a[3], b = false, c = c3, sum = out[3], carry = c4);

FullAdder(a = a[4], b = false, c = c4, sum = out[4], carry = c5);

FullAdder(a = a[5], b = false, c = c5, sum = out[5], carry = c6);

FullAdder(a = a[6], b = false, c = c6, sum = out[6], carry = c7);

FullAdder(a = a[7], b = false, c = c7, sum = out[7], carry = c8);

FullAdder(a = a[8], b = false, c = c8, sum = out[8], carry = c9);

FullAdder(a = a[9], b = false, c = c9, sum = out[9], carry = c10);

FullAdder(a = a[10], b = false, c = c10, sum = out[10], carry = c11);

FullAdder(a = a[11], b = false, c = c11, sum = out[11], carry = c12);

FullAdder(a = a[12], b = false, c = c12, sum = out[12], carry = c13);

FullAdder(a = a[13], b = false, c = c13, sum = out[13], carry = c14);

FullAdder(a = a[14], b = false, c = c14, sum = out[14], carry = c15);

FullAdder(a = a[15], b = false, c = c15, sum = out[15], carry = c16);

}

}}}

* ALU

{{{

}}}

=== 다음 시간까지 공부해올 것 ===

* chapter 3 공부해오기.

=== 후기 ===

* 이제 곧 CPU가 만들어지는건가여.. ㅋㅋ -[김태진]

* ALU는 최곱니다. 이 말밖에 (이번 스터디를) 대체할 말이 없군요. - [김윤환]

* 스터디에 필요한 책 구입해서 비치해두었습니다. - [김민재]

== 11/3(일요일) ==

* 참여자 : [권영기], [김윤환]

=== 공부 내용 ===

* Chapter 4

* Hack Machine language를 사용해서 프로그램을 작성해 봄.

D - data, A - address, M - memory

e.g. A - 32일경우, M은 M[32]임. M을 사용할 때, A의 값은 memory의 address

2개의 Instruction을 지원한다. 각 Instruction은 2Byte이다.

* A-Instruction : @value // Where value is either a non-negative decimal number or a symbol referring to such number.

Binary : 0vvv vvvv vvvv vvvv

* C-Instruction : dest=comp;jump // Either the dest or jump fields may be empty.

// If dest is empty, the "=" is omitted;

// if jump is empty, the ";" is omitted;

{ comp }{dest }{jump}

Binary : 111a c1c2c3c4 c5c6d1d2 d3j1j2j3

* A-instruction 을 사용하면, value는 A에 들어간다.

A의 값이 M이 사용될 때는, 주소의 역할을 하고, D와 같이 사용할 때는 값 그 자체로 작용함.

* [http://nand2tetris.org/chapters/chapter%2004.pdf Chapter4 책 내용]

* [http://nand2tetris.org/lectures/PDF/lecture%2004%20machine%20language.pdf PPT 내용]

=== 실습 과제 ===

* [http://nand2tetris.org/04.php 실습 과제]

* 1 ~ 100까지 더하기 (권영기)

{{{

0 @100

1 M=1

2 @150

3 M=0

4 @100

5 D=M

6 @100

7 D=D-A

8 @18

9 D;JGT

10 @100

11 D=M

12 @150

13 M=D+M

14 @100

15 M=M+1

16 @4

17 0;JMP

18 @18

19 0;JMP

}}}

* 두 수의 곱 (권영기)

{{{

//Memory[10] = A

//Memory[11] = B

//Memory[12] = Dest

0 @20

1 D=A

2 @10

3 M=D

4 @20

5 D=A

6 @11

7 M=D

8 @12

9 M=0

10 @11

11 D=M

12 @22

13 D;JEQ

14 @10

15 D=M

16 @12

17 M=D+M

18 @11

19 M=M-1

20 @10

21 0;JMP

22 @22

23 0;JMP

}}}

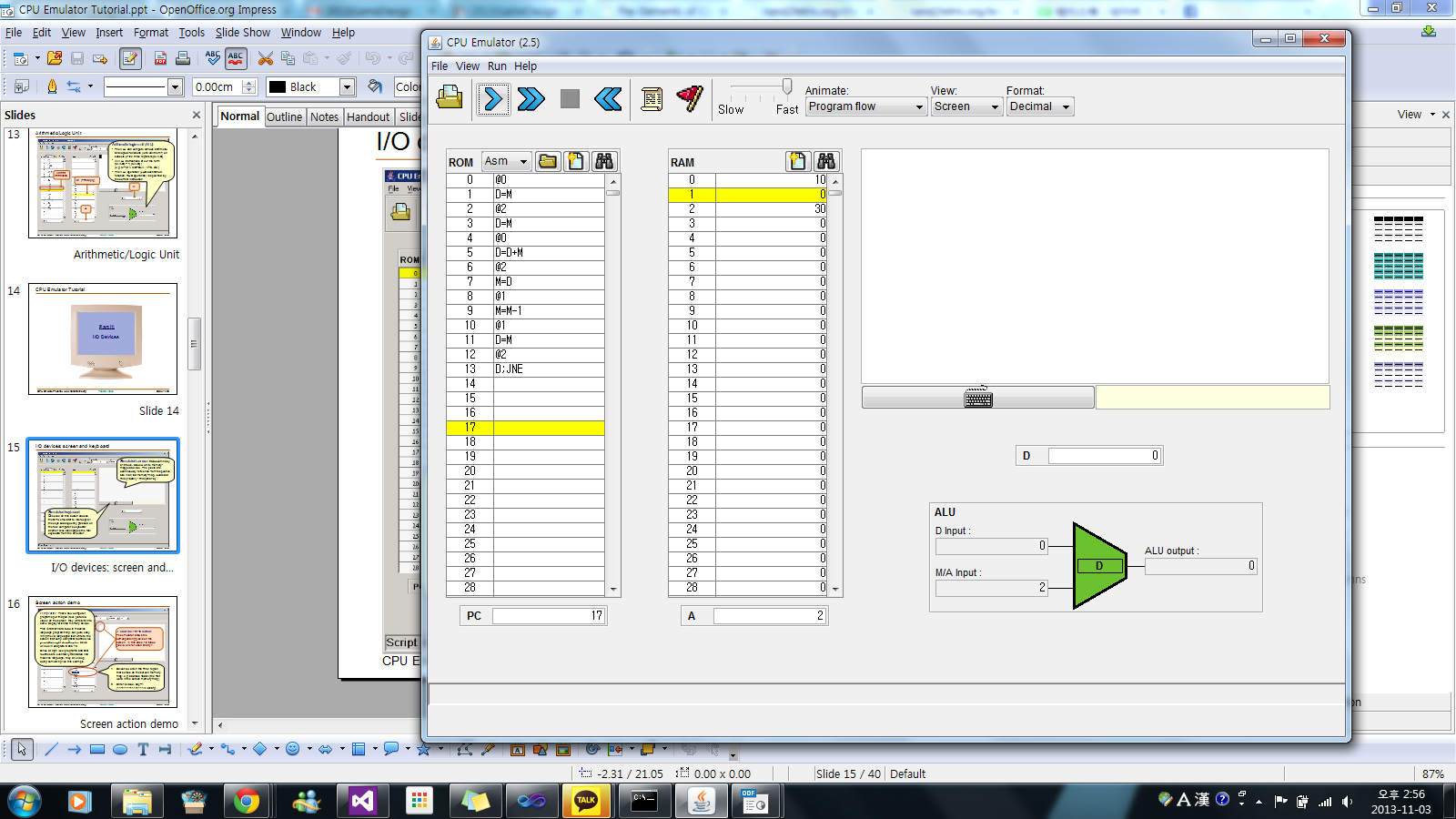

* 두 수의 곱 (김윤환)

attachment:img.png

* I/O Handling, (권영기)(BLACK을 입력하면 네모가 화면에 나오고, WHITE를 입력하면 화면의 네모를 지움)

{{{

0 @24576

1 D=M

2 @0

3 D;JEQ

4 @66

5 D=D-A

6 @1000

7 D;JEQ

8 @24576

9 D=M

10 @87

11 D=D-A

12 @2000

13 D;JEQ

14 @0

15 0;JMP

1000 @24576

1001 D=M

1002 @1000

1003 D;JEQ

1004 @76

1005 D=D-A

1006 @0

1007 D;JNE

1008 @24576

1009 D=M

1010 @1008

1011 D;JEQ

1012 @65

1013 D=D-A

1014 @0

1015 D;JNE

1016 @24576

1017 D=M

1018 @1016

1019 D;JEQ

1020 @67

1021 D=D-A

1022 @0

1023 D;JNE

1024 @24576

1025 D=M

1026 @1024

1027 D;JEQ

1028 @75

1029 D=D-A

1030 @0

1031 D;JNE

1032 @24555

1033 M=-1

1034 @0

1035 0;JMP

2000 @24576

2001 D=M

2002 @2000

2003 D;JEQ

2004 @72

2005 D=D-A

2006 @0

2007 D;JNE

2008 @24576

2009 D=M

2010 @2008

2011 D;JEQ

2012 @73

2013 D=D-A

2014 @0

2015 D;JNE

2016 @24576

2017 D=M

2018 @2016

2019 D;JEQ

2020 @84

2021 D=D-A

2022 @0

2023 D;JNE

2024 @24576

2025 D=M

2026 @2024

2027 D;JEQ

2028 @69

2029 D=D-A

2030 @0

2031 D;JNE

2032 @24555

2033 M=0

2034 @0

2035 0;JMP

}}}

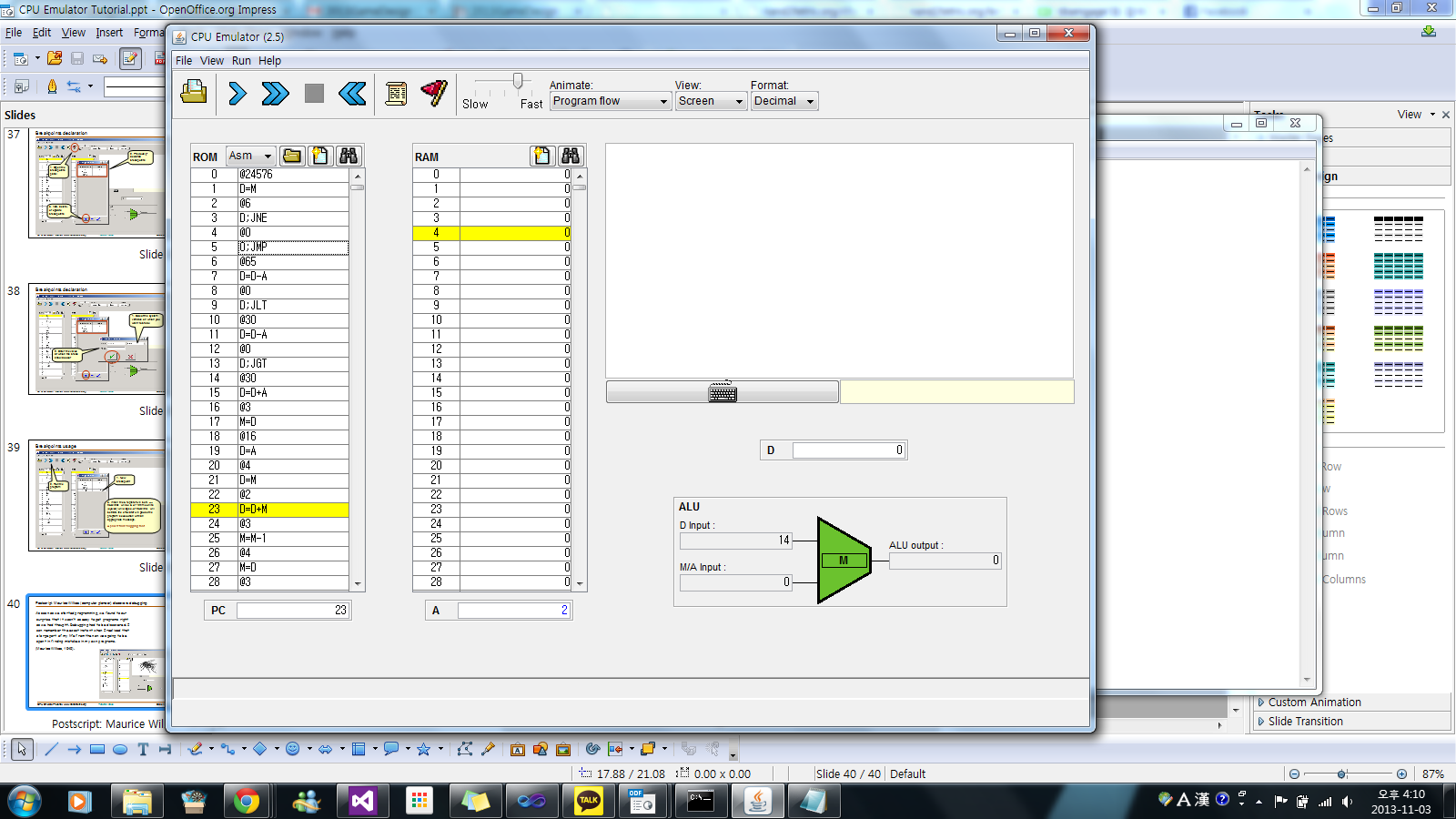

* I/O Handling, (김윤환)(BLACK을 입력하면 네모가 화면에 나오고, WHITE를 입력하면 화면의 네모를 지움)

attachment:sample.png

=== 후기 ===

* MIPS 코딩하는 것을 생각하고 과제를 진행했는데, 현실은 MIPS 보다 더 하드코어했네요. Symbol도 사용안하고(사실 Cpu emulator만 사용해서 생긴 문제일 수도 있지만), 레지스터도 2~3개 밖에 사용하지 못하는 상황에서 작성하려고 하니 참 막막했습니다. I/O Handling 같은 경우 키보드 입력을 해결하려고 나름 생각을 해서 작성을 했는데, 결과물이 영 마음에 들지 않는군요. 아무튼 이번 시간에 느낀 것은 "High-Level Language가 왜 필요한가?" 가 되겠습니다. 사실 이 느낌은 어셈블리 시간에도, 컴퓨터 구조 시간에도 느꼈지만 말이죠. 이제 1/3정도를 진행했고, 계획대로라면 12월이 되기 전까지 1/2는 진행할 수 있을 것 같아서 기분이 좋네요. 무사히 진행해서 끝을 봤으면 하는 생각입니다. - [권영기]

=== 다음에 해야할 일 ===

* Chapter 5를 읽어옵시다.

== 11/17(일요일) ==

* 참여자 : [권영기], [김윤환], [안혁준]

=== 공부 내용 ===

* Von Neumann machine (circa 1940)

Memory (data + instruction) + CPU(ALU + Registers + Control) + Input device & Output device

지금까지 기본적인 논리 게이트를 (Nand만 사용해서) 구현하고, Combinational Chip 과 Sequential Chip까지 전부 구현했다. 지금까지 구현한 것을 모두 합치면 Computer Architecture가 만들어진다.

* The Hack Computer

A 16-bit Von Neumann platform

The instruction memory and the data memory are physically separate

Screen: 512 rows by 256 columns, black and white

Keyboard: standard

* Instruction memory(ROM)

ROM에는 미리 넣어 놓은 프로그램이 있음.

ROM에서는 항상 16bit의 명령어가 나옴.

instruction = ROM32K[address]

* Memory(RAM)

Data memory

읽기

k = address

out = RAM[k]

쓰기

k = address

x = in

load = 1

RAM[k] = x

Screen(memory map)

Screen을 위한 RAM 어딘가를 할당해놓음. 이 공간은 Screen을 위한 공간. CPU는 그 공간을 읽거나 써서 Screen 출력

Keyboard(memory map)

Keyboard를 위한 RAM 어딘가를 할당해놓음. 이 공간은 Keyboard를 위한 공간. CPU는 그 공간을 읽어서 어떤 key가 들어왔는지 확인.

* CPU

* Computer (위의 모든 logic을 다 가지고 있음)

자세한 설명은 [http://nand2tetris.org/lectures/PDF/lecture%2005%20computer%20architecture.pdf architecture] 에 나와있다.

----[2013년활동지도]

1. Nand2Tetris ¶

- 스터디 소개 :

- 컴퓨터의 최하위 레벨 계층인 논리회로(하드웨어)단부터 OS와 high level language까지 두루두루 섭렵하고 실습하여 최종에는 테트리스를 만드는것이 목표인 스터디입니다.

- 컴퓨터의 최하위 레벨 계층인 논리회로(하드웨어)단부터 OS와 high level language까지 두루두루 섭렵하고 실습하여 최종에는 테트리스를 만드는것이 목표인 스터디입니다.

- 스터디에 사용하는 사이트 -> http://www.nand2tetris.org/

1.2.1. 공부한 내용 ¶

- Chapter1

- 기본적인 논리 게이트를 공부함.

- Nand gate를 primitive gate로 놓고, 나머지 논리 게이트 Not, And, Or, Xor, Mux, Demux 등을 Nand만으로 구현.

- Mux나 Demux같은 경우, 입력이나 출력이 너무 많을 경우, 작은 규모의 Mux를 여러 개 이용해서 큰 규모의 Mux를 구현해도 된다. 예를 들면, 4way Mux는 2Way Mux 3개를 이용해서 구현할 수 있다.

- HDL Code

- Not Gate

CHIP Not2 {

IN a;

OUT out;

PARTS:

Nand(a = a, b = a, out = out);

}

- And Gate

CHIP And {

IN a, b;

OUT out;

PARTS:

Nand(a = a, b = b, out = x);

Nand(a = x, b = x, out = out);

}

- Or Gate

CHIP Or {

IN a, b;

OUT out;

PARTS:

Nand(a = a, b = a, out = x1);

Nand(a = b, b = b, out = x2);

Nand(a = x1, b = x2, out = out);

}

- Xor Gate

CHIP Xor {

IN a, b;

OUT out;

PARTS:

Nand(a = a, b = a, out = nota);

Nand(a = b, b = b, out = notb);

Nand(a = nota, b = b, out = x1);

Nand(a = a, b = notb, out = x2);

Nand(a = x1, b = x2, out = out);

}

- Mux

CHIP Mux {

IN a, b, s;

OUT out;

PARTS:

Nand(a = s, b = s, out = nots);

Nand(a = a, b = s, out = x1);

Nand(a = b, b = nots, out = x2);

Nand(a = x1, b = x2, out = out);

}

- Mux 4way

CHIP Mux4way {

IN a[4], s[2];

OUT out;

PARTS:

Nand(a = s[0], b = s[0], out = nots0);

Nand(a = s[1], b = s[1], out = nots1);

Nand(a = a[0], b = s[1], out = x0);

Nand(a = a[1], b = nots1, out = x1);

Nand(a = a[2], b = s[1], out = x2);

Nand(a = a[3], b = nots1, out = x3);

Nand(a = x0, b = x1, out = xx0);

Nand(a = x2, b = x3, out = xx1);

Nand(a = xx0, b = s[0], out = xxx0);

Nand(a = xx1, b = nots0, out = xxx1);

Nand(a = xxx0, b = xxx1, out = out);

}

- Demux

Demux는 다 구현하고서 Mux 4way를 Demux 파일에 써버리는 바람에 날려버림 ㅡㅡ;

1.2.3. 후기 ¶

- 쇠뿔도 단김에 빼라는 말이 있듯이, 순식간에 스터디 진행합니다. 학기 끝날 때까지 매주 진행해보려고 하는데, 끝까지 다 할 수 있었으면 좋겠습니다. 뭐 윤환이나 혁준이형 있으니까 잘 진행되겠죠. 이번 시간에 했던 것은 기초 중에 기초인데, 사실 작년 논리회로 시간에 Nand 게이트로 다른 gate 구현하기 따위는 해본적이 없어서 좀 당황도 했습니다. 그리고 그림 그리는 것도 참 간만이고, 다음 시간까지 논리회로 ppt 좀 보고서 와야겠네요. 간단한 4way MUX도 저리 긴데, 사칙연산은 어떻게 해야할지.. 머리가 아픕니다. - 권영기

- 간만에 논리회로를 다루면서 내가 까먹고 있던 부분이 많다고 느낌니다. 물론 추상화라는 좋은 녀석이 있어서 우리가 모든것을 기억할 필요는 없지만, 그래도 원리를 안다고 해서 안좋을 것 없을듯하네요. nand로 시작해서 nand로 끝나는 시간이었습니다. - 안혁준

- 지금은 처음부분이라 무난하게 진행했지만... 가면갈수록 어떤식으로 진행될지 난이도에 따라서 왠지 바뀔수도 있으려나...하는 생각이 들었습니다. 그나저나 논리회로 뒷부분은 거의 기억이 없는데... 전공책한번 훝어보고 와야할것같습니다. - 김윤환

1.3.1. 공부 내용 ¶

- half-adder, full-adder, 16bit-adder, incremental adder, ALU에 대해서 공부하고 구현하였습니다.

- Half-Adder

CHIP HalfAdder {

IN a, b; // 1-bit inputs

OUT sum, // Right bit of a + b

carry; // Left bit of a + b

PARTS:

And(a = a, b = b, out = carry);

Xor(a = a, b = b, out = sum);

}

- Full-Adder

CHIP FullAdder{

IN a, b, c; // 1-bit inputs

OUT sum, // Right bit of a + b + c

carry; // Left bit of a + b + c

PARTS:

// Put you code here:

Xor(a=a, b=b, out=s1);

And(a=a, b=b, out=c1);

Xor(a=s1, b=c, out=sum);

And(a=s1, b=c, out=c2);

Or(a=c1, b=c2, out=carry);

}

- 16bit Adder

CHIP Add16 {

IN a[16], b[16];

OUT out[16];

PARTS:

FullAdder(a = a[0], b = b[0], c = false, sum = out[0], carry = c1);

FullAdder(a = a[1], b = b[1], c = c1, sum = out[1], carry = c2);

FullAdder(a = a[2], b = b[2], c = c2, sum = out[2], carry = c3);

FullAdder(a = a[3], b = b[3], c = c3, sum = out[3], carry = c4);

FullAdder(a = a[4], b = b[4], c = c4, sum = out[4], carry = c5);

FullAdder(a = a[5], b = b[5], c = c5, sum = out[5], carry = c6);

FullAdder(a = a[6], b = b[6], c = c6, sum = out[6], carry = c7);

FullAdder(a = a[7], b = b[7], c = c7, sum = out[7], carry = c8);

FullAdder(a = a[8], b = b[8], c = c8, sum = out[8], carry = c9);

FullAdder(a = a[9], b = b[9], c = c9, sum = out[9], carry = c10);

FullAdder(a = a[10], b = b[10], c = c10, sum = out[10], carry = c11);

FullAdder(a = a[11], b = b[11], c = c11, sum = out[11], carry = c12);

FullAdder(a = a[12], b = b[12], c = c12, sum = out[12], carry = c13);

FullAdder(a = a[13], b = b[13], c = c13, sum = out[13], carry = c14);

FullAdder(a = a[14], b = b[14], c = c14, sum = out[14], carry = c15);

FullAdder(a = a[15], b = b[15], c = c15, sum = out[15], carry = c16);

}

- Incremental

CHIP Inc16 {

IN a[16];

OUT out[16];

PARTS:

FullAdder(a = a[0], b = false, c = true, sum = out[0], carry = c1);

FullAdder(a = a[1], b = false, c = c1, sum = out[1], carry = c2);

FullAdder(a = a[2], b = false, c = c2, sum = out[2], carry = c3);

FullAdder(a = a[3], b = false, c = c3, sum = out[3], carry = c4);

FullAdder(a = a[4], b = false, c = c4, sum = out[4], carry = c5);

FullAdder(a = a[5], b = false, c = c5, sum = out[5], carry = c6);

FullAdder(a = a[6], b = false, c = c6, sum = out[6], carry = c7);

FullAdder(a = a[7], b = false, c = c7, sum = out[7], carry = c8);

FullAdder(a = a[8], b = false, c = c8, sum = out[8], carry = c9);

FullAdder(a = a[9], b = false, c = c9, sum = out[9], carry = c10);

FullAdder(a = a[10], b = false, c = c10, sum = out[10], carry = c11);

FullAdder(a = a[11], b = false, c = c11, sum = out[11], carry = c12);

FullAdder(a = a[12], b = false, c = c12, sum = out[12], carry = c13);

FullAdder(a = a[13], b = false, c = c13, sum = out[13], carry = c14);

FullAdder(a = a[14], b = false, c = c14, sum = out[14], carry = c15);

FullAdder(a = a[15], b = false, c = c15, sum = out[15], carry = c16);

}

- ALU

1.4.1. 공부 내용 ¶

- Chapter 4

- Hack Machine language를 사용해서 프로그램을 작성해 봄.

D - data, A - address, M - memory

e.g. A - 32일경우, M은 M32임. M을 사용할 때, A의 값은 memory의 address

2개의 Instruction을 지원한다. 각 Instruction은 2Byte이다.

- A-Instruction : @value // Where value is either a non-negative decimal number or a symbol referring to such number.

Binary : 0vvv vvvv vvvv vvvv

- C-Instruction : dest=comp;jump // Either the dest or jump fields may be empty.

// If dest is empty, the "=" is omitted;

// if jump is empty, the ";" is omitted;

- A-instruction 을 사용하면, value는 A에 들어간다.

A의 값이 M이 사용될 때는, 주소의 역할을 하고, D와 같이 사용할 때는 값 그 자체로 작용함.

- Chapter4 책 내용

- PPT 내용

{ comp }{dest }{jump}

Binary : 111a c1c2c3c4 c5c6d1d2 d3j1j2j3

1.4.2. 실습 과제 ¶

- 실습 과제

- 1 ~ 100까지 더하기 (권영기)

0 @100 1 M=1 2 @150 3 M=0 4 @100 5 D=M 6 @100 7 D=D-A 8 @18 9 D;JGT 10 @100 11 D=M 12 @150 13 M=D+M 14 @100 15 M=M+1 16 @4 17 0;JMP 18 @18 19 0;JMP

- 두 수의 곱 (권영기)

//Memory[10] = A //Memory[11] = B //Memory[12] = Dest 0 @20 1 D=A 2 @10 3 M=D 4 @20 5 D=A 6 @11 7 M=D 8 @12 9 M=0 10 @11 11 D=M 12 @22 13 D;JEQ 14 @10 15 D=M 16 @12 17 M=D+M 18 @11 19 M=M-1 20 @10 21 0;JMP 22 @22 23 0;JMP

- 두 수의 곱 (김윤환)

[PNG image (303.11 KB)]

- I/O Handling, (권영기)(BLACK을 입력하면 네모가 화면에 나오고, WHITE를 입력하면 화면의 네모를 지움)

0 @24576 1 D=M 2 @0 3 D;JEQ 4 @66 5 D=D-A 6 @1000 7 D;JEQ 8 @24576 9 D=M 10 @87 11 D=D-A 12 @2000 13 D;JEQ 14 @0 15 0;JMP 1000 @24576 1001 D=M 1002 @1000 1003 D;JEQ 1004 @76 1005 D=D-A 1006 @0 1007 D;JNE 1008 @24576 1009 D=M 1010 @1008 1011 D;JEQ 1012 @65 1013 D=D-A 1014 @0 1015 D;JNE 1016 @24576 1017 D=M 1018 @1016 1019 D;JEQ 1020 @67 1021 D=D-A 1022 @0 1023 D;JNE 1024 @24576 1025 D=M 1026 @1024 1027 D;JEQ 1028 @75 1029 D=D-A 1030 @0 1031 D;JNE 1032 @24555 1033 M=-1 1034 @0 1035 0;JMP 2000 @24576 2001 D=M 2002 @2000 2003 D;JEQ 2004 @72 2005 D=D-A 2006 @0 2007 D;JNE 2008 @24576 2009 D=M 2010 @2008 2011 D;JEQ 2012 @73 2013 D=D-A 2014 @0 2015 D;JNE 2016 @24576 2017 D=M 2018 @2016 2019 D;JEQ 2020 @84 2021 D=D-A 2022 @0 2023 D;JNE 2024 @24576 2025 D=M 2026 @2024 2027 D;JEQ 2028 @69 2029 D=D-A 2030 @0 2031 D;JNE 2032 @24555 2033 M=0 2034 @0 2035 0;JMP

- I/O Handling, (김윤환)(BLACK을 입력하면 네모가 화면에 나오고, WHITE를 입력하면 화면의 네모를 지움)

[PNG image (300.59 KB)]

1.4.3. 후기 ¶

- MIPS 코딩하는 것을 생각하고 과제를 진행했는데, 현실은 MIPS 보다 더 하드코어했네요. Symbol도 사용안하고(사실 Cpu emulator만 사용해서 생긴 문제일 수도 있지만), 레지스터도 2~3개 밖에 사용하지 못하는 상황에서 작성하려고 하니 참 막막했습니다. I/O Handling 같은 경우 키보드 입력을 해결하려고 나름 생각을 해서 작성을 했는데, 결과물이 영 마음에 들지 않는군요. 아무튼 이번 시간에 느낀 것은 "High-Level Language가 왜 필요한가?" 가 되겠습니다. 사실 이 느낌은 어셈블리 시간에도, 컴퓨터 구조 시간에도 느꼈지만 말이죠. 이제 1/3정도를 진행했고, 계획대로라면 12월이 되기 전까지 1/2는 진행할 수 있을 것 같아서 기분이 좋네요. 무사히 진행해서 끝을 봤으면 하는 생각입니다. - 권영기

1.5.1. 공부 내용 ¶

- Von Neumann machine (circa 1940)

Memory (data + instruction) + CPU(ALU + Registers + Control) + Input device & Output device

지금까지 기본적인 논리 게이트를 (Nand만 사용해서) 구현하고, Combinational Chip 과 Sequential Chip까지 전부 구현했다. 지금까지 구현한 것을 모두 합치면 Computer Architecture가 만들어진다.

- The Hack Computer

A 16-bit Von Neumann platform

The instruction memory and the data memory are physically separate

Screen: 512 rows by 256 columns, black and white

Keyboard: standard

- Instruction memory(ROM)

ROM에는 미리 넣어 놓은 프로그램이 있음.

ROM에서는 항상 16bit의 명령어가 나옴.

instruction = ROM32Kaddress

- Memory(RAM)

Data memory

읽기

k = address

out = RAMk

쓰기

- CPU

- Computer (위의 모든 logic을 다 가지고 있음)

자세한 설명은 architecture 에 나와있다.

k = address

x = in

load = 1

RAMk = x

Screen(memory map)

Screen을 위한 RAM 어딘가를 할당해놓음. 이 공간은 Screen을 위한 공간. CPU는 그 공간을 읽거나 써서 Screen 출력

x = in

load = 1

RAMk = x

Screen(memory map)

Screen을 위한 RAM 어딘가를 할당해놓음. 이 공간은 Screen을 위한 공간. CPU는 그 공간을 읽거나 써서 Screen 출력

Keyboard(memory map)

Keyboard를 위한 RAM 어딘가를 할당해놓음. 이 공간은 Keyboard를 위한 공간. CPU는 그 공간을 읽어서 어떤 key가 들어왔는지 확인.

Keyboard를 위한 RAM 어딘가를 할당해놓음. 이 공간은 Keyboard를 위한 공간. CPU는 그 공간을 읽어서 어떤 key가 들어왔는지 확인.